# 經濟部智慧財產局一○一年度 委託研究計畫

資訊產業專利趨勢與專利訴訟分析研究計畫

資訊產業廠商在美國專利訴訟案件分析

10件專利訴訟案件分析報告

(LG v. Quanta)

主辦單位:經濟部智慧財產局

執行單位:台灣科技法學會

中華民國101年12月

契約編號:10018008020

# 經濟部智慧財產局

資訊產業專利趨勢與專利訴訟分析研究計畫

資訊產業廠商在美國專利訴訟案件分析

10件專利訴訟案件分析報告

計畫主持人:劉尚志

協同主持人:鄭猷超

研究者: 陳在方、陳瑋明、林曉涵、楊佩錡、林耕文

劉思伶、劉威克、李 玄、洪紹庭、吳佩珊

陳捷安、張嘉顯、龔鈺芬

中華民國101年12月

# 目錄

# 上册

| 第  | 一章  | 案件篩選                     | 1   |

|----|-----|--------------------------|-----|

|    | 第一節 | 前言                       | 1   |

|    | 第二節 | 資料來源與篩選目標                | 4   |

| 1. | 資   | 料來源                      | 4   |

| 2. | 案   | 件篩選策略                    | 18  |

| 3. | 10  | ) 案件中選原因                 | 25  |

|    | 第三節 | 專利策略與管理議題之案件             | 36  |

|    | 第四節 | 程序與訴訟技巧之案件               | 42  |

|    | 第五節 | 專利訴訟爭議之案件                | 45  |

| 第  | 二章  | 案件分析                     | 48  |

|    | 第一節 | Apple v. HTC             | 48  |

| 1. | 前   | - <u>+</u>               | 48  |

| 2. |     | 件基礎資料                    | 49  |

| 3. |     | 件簡介                      | 51  |

|    | 3.1 | 本案事實                     | 51  |

|    | 3.2 | <b>两造背景</b>              | 51  |

|    | 3.3 | 本案主要程序進行時程               | 51  |

|    | 3.4 | 本案系爭專利、系爭產品、有效性引證技術內容    | 53  |

| 4  | 案   | 件分析                      | 71  |

|    | 4.1 | 申請專利範圍解釋                 | 71  |

|    | 4.2 | 侵權                       | 117 |

|    | 4.3 | 國內產業                     | 137 |

|    | 4.4 | 專利有效性                    | 140 |

| 5  | 本   | 案評析                      | 145 |

|    | 5.1 | 實體爭議                     | 145 |

|    | 5.2 | 程序攻防                     | 148 |

|    | 5.3 | 專利訴訟策略                   | 149 |

|    | 第二節 | Philips Lumileds v. 晶元光電 | 152 |

| 1. | 前   | 吉                        | 152 |

| 2. |     | 件基礎資料                    | 154 |

| 3. |     | 件簡介                      | 155 |

|    | 3.1 | 本案事實                     | 155 |

|    | 3.2 | <b>两造背景</b>              | 156 |

|    | 3.3 | 本案主要程序進行時程               | 157 |

|    | 3.4 | 本案系爭專利、系爭產品技術內容          | 158 |

#### 目錄

| 4. | 案   | 件分析                       | 160        |

|----|-----|---------------------------|------------|

|    | 4.1 | 申請專利範圍解釋                  | 160        |

|    | 4.2 | 本訴告訴人晶元光電得否主張系爭'718 號專利無效 | 167        |

| 5. | 本   | 案評析                       | 176        |

|    | 5.1 | 實體爭議                      | 176        |

|    | 5.2 | 程序攻防                      | 177        |

|    | 5.3 | 專利訴訟策略                    | 178        |

|    | 第三節 | LG v. Quanta              | 180        |

| 1. |     |                           | 180        |

| 2. |     | 4件基礎資料                    | 181        |

|    |     | 一審                        | 181        |

|    |     | 二審                        | 182        |

| _  | 2.3 | 三審                        | 184        |

| 3. |     | (件簡介                      | 185        |

|    | 3.1 | 本案事實                      | 185        |

|    |     | 丙造背景<br>                  | 186        |

|    | 3.3 | 本案主要程序進行時程                | 186        |

|    | 3.4 | 本案系爭專利、系爭產品技術內容           | 187        |

| 4. |     | 件分析                       | 199        |

|    | 4.1 | 申請專利範圍解釋(於最高法院爭訟之三項專利)    | 200        |

|    | 4.2 | 一審                        | 240        |

|    | 4.3 | 二審                        | 243        |

|    | 4.4 | 三審                        | 246        |

| 5. |     | <b>案評析</b>                | 252        |

|    | 5.1 | 實體爭議                      | 252        |

|    | 5.2 | 程序攻防                      | 253        |

|    | 5.3 | 專利訴訟的策略                   | 253        |

|    |     | 理光 v. 廣達等                 | 256        |

| 1. |     | 言                         | 256        |

| 2. |     | #件基礎資料<br>#件簡介            | 257<br>258 |

|    | 3.1 | 本案事實                      | 258        |

|    | 3.2 | <b>两造背景</b>               | 258        |

|    | 3.3 | 本案主要程序進行時程                | 259        |

|    | 3.4 | 本案系爭專利、系爭產品、有效性引證技術內容     | 260        |

| 4. | 案   | 件分析                       | 276        |

|    | 4.1 | 系爭專利請求項整理表                | 276        |

|    | 4.2 | 法院判決結果整理表                 | 280        |

|    | 4.3 | 法院對於'109 號專利有效性之認定        | 280        |

|    | 4.4 | 直接侵權:廣達對於'955 專利不構成直接侵權   | 286        |

|    | 4.5      | 直接侵權:廣達與 NU Technology 對於'552、'755 專利皆不構成直接侵權            | 289        |

|----|----------|----------------------------------------------------------|------------|

|    | 4.6      | 輔助侵權 (Contributory Infringement): 廣達對於'552、'755 專利構成輔助侵權 | 293        |

|    | 4.7      | 誘引侵權 (Induced Infringement):廣達對於'552、'755 專利構成誘引侵權       | 298        |

|    | 4.8      | 陪審團評決:廣達須對間接侵權負損害賠償責任                                    | 303        |

| 5. | 本        | 案評析                                                      | 303        |

|    | 5.1      | 實體爭議                                                     | 303        |

|    | 5.2      | 專利訴訟策略                                                   | 305        |

|    | 第五節      | Nokia v. Apple                                           | 307        |

| 1. |          | <u></u>                                                  | 307        |

| 2. |          | t件基礎資料<br>- M - S - A - S - S - S - S - S - S - S - S    | 308        |

| 3. | 系<br>3.1 | ·件簡介<br>本案事實                                             | 309        |

|    | 3.2      | 两造背景                                                     | 317        |

|    | 3.3      | 本案主要程序進行時程                                               | 318        |

|    |          |                                                          |            |

| 4. | 3.4<br>安 | 本案系爭專利、系爭產品技術內容<br>件分析                                   | 320<br>342 |

| ᅻ. | 4.1      |                                                          | 342        |

|    | 4.2      | 駁回反訴及抗辯之裁定                                               | 344        |

| 5. |          | 件評析                                                      | 347        |

|    | 5.1      | 實體爭議                                                     | 347        |

|    | 5.2      | 程序攻防                                                     | 349        |

|    | 5.3      | 專利訴訟策略                                                   | 350        |

|    |          | 下冊                                                       |            |

|    | 第六節      | Immersion v. Sony                                        | 354        |

| 1. | 前        | - <u>-</u> -                                             | 354        |

| 2. |          | 件基礎資料                                                    | 355        |

| 3. |          | · 件簡介                                                    | 356        |

|    | 3.1      | 本案事實                                                     | 356        |

|    | 3.2      | 两造背景<br>                                                 | 357        |

|    | 3.3      | 本案主要程序進行時程                                               | 358        |

| 1  | 3.4      | 本案系爭專利、系爭產品、有效性引證技術內容                                    | 359        |

| 4. | 条<br>4.1 | 件分析<br>申請專利範圍解釋                                          | 377<br>377 |

|    | 4.2      | 即決判決                                                     | 399        |

|    | 4.2      | 陪審團評決                                                    | 410        |

|    | 4.3      | 第三人交叉訴訟                                                  | 420        |

|    | 4.5      | 不公平行為判決                                                  | 425        |

|    | 4.6      | 再審                                                       | 431        |

| 5. |          | <del>背面</del><br>案評析                                     | 438        |

|    | · T      |                                                          |            |

|    | 5.1 實體爭議                                   | 438 |

|----|--------------------------------------------|-----|

|    | 5.2 專利訴訟策略                                 | 442 |

|    | 第七節 緯創 v. 三星                               | 443 |

| 1. | . 前言                                       | 443 |

| 2. | . 案件基礎資料                                   | 444 |

| 3. | . 案件簡介                                     | 445 |

|    | 3.1 本案事實                                   | 445 |

|    | 3.2 兩造背景                                   | 445 |

|    | 3.3 本案主要程序進行時程                             | 447 |

|    | 3.4 本案系爭專利、系爭產品介紹、有效性引證技術內容                | 448 |

| 4. | . 案件分析                                     | 472 |

|    | 4.1 申請專利範圍解釋                               | 472 |

|    | 4.2 系爭 3 個專利之總體有效性分析                       | 520 |

|    | 4.3 系爭 3 個專利於 35 U.S.C. §102 規範下有效性之即決判決聲請 | 527 |

|    | 4.4 就'273 號專利以及'100 號專利可執行性聲請即決判決          | 539 |

| 5. | . 本案評析                                     | 545 |

|    | 5.1 實體爭議                                   | 545 |

|    | 5.2 程序攻防                                   | 552 |

|    | 5.3 專利訴訟策略                                 | 553 |

|    | 第八節 義隆 v. 蘋果                               | 554 |

| 1. | . 前言                                       | 554 |

| 2. | . 案件基礎資料                                   | 556 |

| 3. | . 案件簡介                                     | 557 |

|    | 3.1 本案事實                                   | 557 |

|    | 3.2 兩造背景                                   | 558 |

|    | 3.3 本案主要程序進行時程                             | 559 |

|    | 3.4 本案系爭專利、系爭產品、有效性引證技術內容                  | 560 |

| 4. | . 案件分析                                     | 565 |

|    | 4.1 申請專利範圍解釋                               | 565 |

|    | 4.2 專利侵權分析                                 | 580 |

|    | 4.3 有效性分析                                  | 586 |

|    | 4.4 國內產業                                   | 591 |

| 5. | . 本案評析                                     | 592 |

|    | 5.1 實體爭議                                   | 592 |

|    | 5.2 程序攻防                                   | 593 |

|    | 5.3 專利訴訟策略                                 | 594 |

|    | 第九節 AMD v. 三星                              | 597 |

| 1. | . 前言                                       | 597 |

| 2. |                                            | 598 |

| 3. | . 案件簡介                                     | 600 |

|    | 3.1 | 本案事實                                             | 600 |

|----|-----|--------------------------------------------------|-----|

|    | 3.2 | 兩造背景                                             | 600 |

|    | 3.3 | 本案主要程序進行時程                                       | 602 |

|    | 3.4 | 本案系爭專利、系爭產品、有效性引證技術內容                            | 603 |

| 4. | 案   | 件分析                                              | 630 |

|    | 4.1 | 被告聲請部分即決判決與保持命令 (Protective Order)               | 630 |

|    | 4.2 | 申請專利範圍解釋                                         | 636 |

|    | 4.3 | 原告聲請無不公平行為即決判決及逕以訴狀判決(Judgment on the Pleadings) | 676 |

|    | 4.4 | 聲請不侵權即決判決之裁定                                     | 689 |

| 5. | 本   | 案評析                                              | 699 |

|    | 5.1 | 實體爭議                                             | 699 |

|    | 5.2 | 程序攻防                                             | 703 |

|    | 5.3 | 專利訴訟策略                                           | 705 |

|    | 第十節 | Thomson Licensing 控告友達等                          | 707 |

| 1. | 前   | 吉                                                | 707 |

| 2. |     | 件基礎資料                                            | 708 |

| 3. |     | 件簡介                                              | 709 |

|    | 3.1 | 本案事實                                             | 710 |

|    | 3.2 | 兩造背景                                             | 710 |

|    | 3.3 | 本案主要程序進行時程                                       | 711 |

|    | 3.4 | 本案系爭專利、系爭產品、有效性引證技術內容                            | 712 |

| 4. | 案   | 件分析                                              | 731 |

|    | 4.1 | 申請專利範圍解釋                                         | 731 |

|    | 4.2 | 侵權判斷                                             | 763 |

|    | 4.3 | 有效性判斷                                            | 773 |

| 5. | 本   | 案評析                                              | 780 |

|    | 5.1 | 實體爭議                                             | 780 |

|    | 5.2 | 程序攻防                                             | 781 |

|    | 5.3 | 專利訴訟策略                                           | 782 |

# 表目錄

| 表 1 觸控應用裝置技術 2002-2011 年美國專利訴訟統計表—台灣廠商涉案件數             | 2   |

|--------------------------------------------------------|-----|

| 表 2 觸控應用裝置於美國專利訴訟調查 (2007 年 1 月 1 日至 2011 年 12 月 31 日) | 5   |

| 表 3 案件篩選表                                              | 18  |

| 表 4 本計畫案件篩選原因整理表                                       | 25  |

| 表 5 APPLE 控告 HTC 案件基礎資料表                               | 49  |

| 表 6 APPLE 控告 HTC 案件主要程序進行時程表                           | 52  |

| 表 7APPLE 控告 HTC'263 號專利兩造論點與法院認定整理表(1)                 | 86  |

| 表 8 APPLE 控告 HTC'263 號專利兩造論點與法院認定整理表(2)                | 89  |

| 表 9 APPLE 控告 HTC'263 號專利兩造論點與法院認定整理表(3)                | 89  |

| 表 10 APPLE 控告 HTC'263 號專利兩造論點與法院認定整理表(4)               | 91  |

| 表 11 APPLE 控告 HTC'647 號專利兩造論點與法院認定整理表(1)               | 93  |

| 表 12 APPLE 控告 HTC'647 號專利兩造論點與法院認定整理表(2)               | 98  |

| 表 13 APPLE 控告 HTC'721 號專利兩造論點與法院認定整理表(1)               | 98  |

| 表 14 APPLE 控告 HTC'721 號專利兩造論點與法院認定整理表(2)               | 107 |

| 表 15 APPLE 控告 HTC'721 號專利兩造論點與法院認定整理表(3)               | 107 |

| 表 16 APPLE 控告 HTC'721 號專利兩造論點與法院認定整理表(4)               | 108 |

| 表 17 APPLE 控告 HTC'983 號專利兩造論點與法院認定整理表(1)               | 110 |

| 表 18 APPLE 控告 HTC'983 號專利兩造論點與法院認定整理表(2)               | 113 |

| 表 19 APPLE 控告 HTC'983 號專利兩造論點與法院認定整理表(3)               | 115 |

| 表 20 APPLE 控告 HTC 專利侵權判決整理表                            | 117 |

| 表 21 案件基礎資料表                                           | 154 |

| 表 22 PHILIPS LUMILED 控告晶元光電主要程序進行時程表                   | 158 |

| 表 23 PHILIPS LUMILED 控告晶元光電 '718 號專利兩造論點與法院認定整理表 (1)   | 163 |

| 表 24 PHILIPS LUMILED 控告晶元光電 '718 號專利兩造論點與法院認定整理表 (2)   | 165 |

| 表 25 LG 控告 QUANTA 一審案件基礎資料表                            | 181 |

| 表 26 LG 控告 QUANTA 二審案件基礎資料表                            | 182 |

| 表 27 LG 控告 QUANTA 三審案件基礎資料表                            | 184 |

| 表 28 LG 控告 QUANTA 主要程序進行時程表                            | 186 |

| 表 29 LG 於一審控告 QUANTA 案'641 號專利兩造論點與法院認定整理表(1)          | 217 |

| 表 30 LG 於一審控告 QUANTA 案'641 號專利兩造論點與法院認定整理表(2)          | 219 |

| 表 31 LG 於一審控告 QUANTA 案'641 號專利兩造論點與法院認定整理表(3)          | 221 |

| 表 32 LG 於一審控告 QUANTA 案'641 號專利兩造論點與法院認定整理表(4)          | 222 |

| 表 33 LG 於一審控告 QUANTA 案'641 號專利兩造論點與法院認定整理表(5)          | 224 |

| 表 34 LG 於一審控告 QUANTA 案'641 號專利兩造論點與法院認定整理表(6)          | 224 |

| 表 35 LG 於一審控告 QUANTA 案'641 號專利兩造論點與法院認定整理表(7)          | 225 |

| 表 36 LG 於一審控告 QUANTA 案'379 號專利兩造論點與法院認定整理表(1)          | 226 |

| 表 37 LG 於一審控告 QUANTA 案'379 號專利兩造論點與法院認定整理表(2)     | 229 |

|---------------------------------------------------|-----|

| 表 38 LG 於一審控告 QUANTA 案'379 號專利兩造論點與法院認定整理表(3)     | 232 |

| 表 39 LG 於一審控告 QUANTA 案'379 號專利兩造論點與法院認定整理表(4)     | 235 |

| 表 40 LG 於一審控告 QUANTA 案'379 號專利兩造論點與法院認定整理表(5)     | 236 |

| 表 41 LG 於一審控告 QUANTA 案'733 號專利兩造論點與法院認定整理表(1)     | 237 |

| 表 42 LG 於一審控告 QUANTA 案'733 號專利兩造論點與法院認定整理表(2)     | 238 |

| 表 43 LG 於一審控告 QUANTA 案'733 號專利兩造論點與法院認定整理表(3)     | 239 |

| 表 44 RICOH 控告廣達案件基礎資料                             | 257 |

| 表 45 NOKIA 控告 APPLE 案件基礎資料表                       | 308 |

| 表 46 NOKIA 控告 APPLE 案件主要程序進行時程表                   | 318 |

| 表 47 IMMERSION 控告 SONY 案件基礎資料                     | 355 |

| 表 48 IMMERSION 控告 SONY 主要程序進行時程表                  | 358 |

| 表 49 IMMERSION 控告 SONY 系爭被控侵權產品一覽表                | 367 |

| 表 50 IMMERSION 控告 SONY'213 號專利兩造論點與法院認定整理表(1)     | 381 |

| 表 51IMMERSION 控告 SONY'213 號專利雨造論點與法院認定整理表(2)      | 383 |

| 表 52IMMERSION 控告 SONY'213、'333 號專利兩造論點與法院認定整理表(3) | 384 |

| 表 53 IMMERSION 控告 SONY'213 號專利兩造論點與法院認定整理表(4)     | 388 |

| 表 54 IMMERSION 控告 SONY'213 號專利兩造論點與法院認定整理表(5)     | 392 |

| 表 55 IMMERSION 控告 SONY'213 號專利兩造論點與法院認定整理表(6)     | 394 |

| 表 56 IMMERSION 控告 SONY'213 號專利兩造論點與法院認定整理表(7)     | 397 |

| 表 57 IMMERSION 控告 SONY'213 號專利兩造論點與法院認定整理表(8)     | 397 |

| 表 58 IMMERSION 控告 SONY 陪審團評決內容表(1)                | 418 |

| 表 59 IMMERSION 控告 SONY 陪審團評決內容表(2)                | 419 |

| 表 60 緯創控告三星案件基礎資料表                                | 444 |

| 表 61 緯創控告三星主要程序進行時程表                              | 447 |

| 表 62 緯創控告三星案'273 號專利兩造論點與法院認定整理表(1)               | 489 |

| 表 63 緯創控告三星案'273 號專利兩造論點與法院認定整理表(2)               | 492 |

| 表 64 緯創控告三星案'273 號專利兩造論點與法院認定整理表(3)               | 494 |

| 表 65 緯創控告三星案'273 號專利兩造論點與法院認定整理表(4)               | 495 |

| 表 66 緯創控告三星案'273 號專利兩造論點與法院認定整理表(5)               | 496 |

| 表 67 緯創控告三星案'273 號專利兩造論點與法院認定整理表(6)               | 499 |

| 表 68 緯創控告三星案'273 號專利兩造論點與法院認定整理表(7)               | 500 |

| 表 69 緯創控告三星案'273 號專利兩造論點與法院認定整理表(8)               | 501 |

| 表 70 緯創控告三星案'273 號專利兩造論點與法院認定整理表(9)               | 502 |

| 表 71 緯創控告三星案'275 號專利兩造論點與法院認定整理表(1)               | 502 |

| 表 72 緯創控告三星案'275 號專利兩造論點與法院認定整理表(2)               | 505 |

| 表 73 緯創控告三星案'275 號專利兩造論點與法院認定整理表(3)               | 507 |

| 表 74 緯創控告三星案'100 號專利兩造論點與法院認定整理表(1)               | 509 |

| 表 75 緯創控告三星案'100 號專利兩造論點與法院認定整理表(2)                  | 513 |

|------------------------------------------------------|-----|

| 表 76 緯創控告三星案'100 號專利兩造論點與法院認定整理表(3)                  | 515 |

| 表 77 緯創控告三星案'100 號專利雨造論點與法院認定整理表(4)                  | 515 |

| 表 78 緯創控告三星案'100 號專利雨造論點與法院認定整理表(5)                  | 517 |

| 表 79 緯創控告三星案'100 號專利雨造論點與法院認定整理表(6)                  | 518 |

| 表 80 義隆控告蘋果案件基礎資料表                                   | 556 |

| 表 81 義隆控告蘋果案件主要程序進行時程表                               | 559 |

| 表 82 義隆控告蘋果'352 號專利兩造論點與法院認定整理表                      | 573 |

| 表 83 義隆控告蘋果'352 號專利侵害比對整理表                           | 580 |

| 表 84 AMD 控告三星案件基礎資料表                                 | 598 |

| 表 85 AMD 控告三星主要程序進行時程表                               | 602 |

| 表 86 AMD 控告三星案'990 號專利雨造論點與法院認定整理表(1)                | 650 |

| 表 87 AMD 控告三星案'990 號專利雨造論點與法院認定整理表(2)                | 652 |

| 表 88 AMD 控告三星案'990 號專利兩造論點與法院認定整理表(3)                | 662 |

| 表 89 AMD 控告三星案'990 號專利兩造論點與法院認定整理表(3)                | 671 |

| 表 90 THOMSON LICENSING 控告友達等案件基礎資料表                  | 708 |

| 表 91 THOMSON LICENSING 控告友達等主要程序進行時程表                | 711 |

| 表 92 THOMSON LICENSING 控告友達等系爭專利請求項整理表               | 732 |

| 表 93 THOMSON LICENSING 控告友達等'063 號專利兩造論點與法院認定整理表 (1) | 753 |

| 表 94 THOMSON LICENSING 控告友達等'063 號專利兩造論點與法院認定整理表 (2) | 755 |

| 表 95 THOMSON LICENSING 控告友達等'063 號專利兩造論點與法院認定整理表 (3) | 756 |

| 表 96 THOMSON LICENSING 控告友達等 ALJ 與委員會侵權判決認定整理表       | 763 |

| 表 97 THOMSON LICENSING 主張友達產品侵害'006 號專利之比對整理表        | 765 |

| 表 98 THOMSON LICENSING 主張友達產品侵害'556 號專利之比對整理表        | 769 |

| 表 99 THOMSON LICENSING 妳生方達筆 ALI 與季昌命有於性對決認定較理表      | 773 |

# 圖目錄

| 圖 1 觸控應用裝置技術 2002-2011 美國專利訴訟統計              | 2   |

|----------------------------------------------|-----|

| 圖 2 觸控應用裝置技術 2002-2011 年美國專利訴訟案統計—台灣廠商涉案件數   | 3   |

| 圖 3 美國專訴訟案例分析流程                              | 4   |

| 圖 4 專利策略管理分析流程                               | 36  |

| 圖 5 程序與訴訟技巧分析流程                              | 42  |

| 圖 6 程序與訴訟技巧分析流程                              | 45  |

| 圖 7 '263 號專利說明書圖 2 系爭發明電腦硬體對應該即時引擎的介面        | 55  |

| 圖 8 '263 號專利說明書圖 3 系爭發明即時引擎的細部架構             | 56  |

| 圖 9 '721 號專利專利說明書圖 1 系爭發明物件導向方法流程圖           | 58  |

| 圖 10 '647 號專利說明書圖 2 系爭發明主要程式圖                | 60  |

| 圖 11 '647 專利說明書圖 7 系爭發明選擇動作之跳出選單             | 61  |

| 圖 12 '983 號專利說明書圖 1 系爭發明操作流程圖                | 63  |

| 圖 13 晶元光電與 PHILIPS LUMILEDS 案件事實簡圖           | 169 |

| 圖 14 '641 號專利說代表圖專利發明之高階方塊圖                  | 188 |

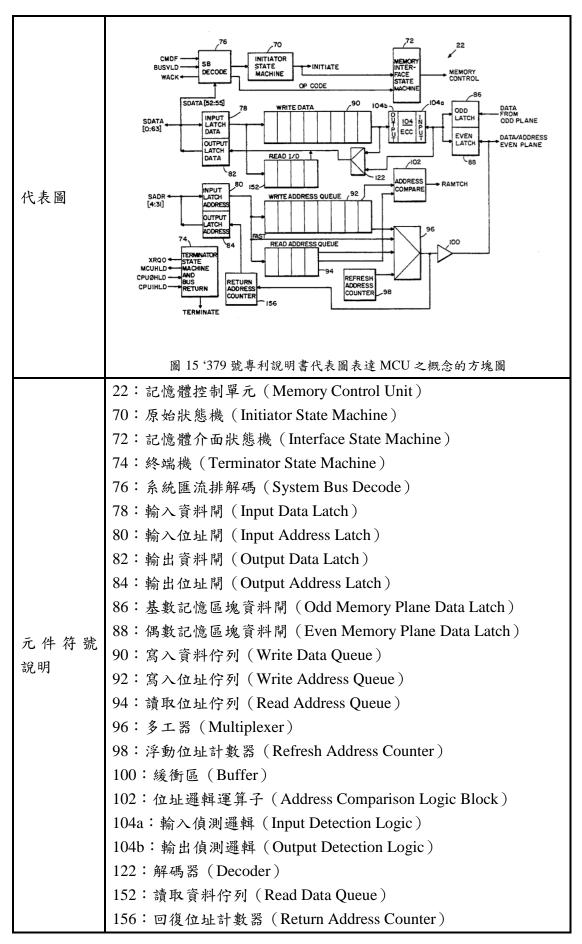

| 圖 15 '379 號專利說明書代表圖表達 MCU 之概念的方塊圖            | 193 |

| 圖 16 '733 號專利說明書代表圖系統結合此發明的方塊圖               | 195 |

| 圖 17 '641 號專利說明書圖 5 當 CPU 寫入資料到記憶體時的決策樹      | 197 |

| 圖 18 '379 號專利說明書圖 2 表達 MCU 的主控制流程之流程圖        | 198 |

| 圖 19 '733 號專利說明書圖 1A、1B 拓撲結構之環狀排列的系統匯流排示意圖   | 199 |

| 圖 20'109 號專利圖 3 本發明之光碟機較佳實施例之流程圖             | 262 |

| 圖 21 '955 號專利說明書圖 1 本發明第一個實施例之光碟機的流程圖        | 264 |

| 圖 22 '552 號專利說明書圖 1 本發明較佳實施例之光碟機,可提供控制系統的流程圖 | 266 |

| 圖 23 '755 號專利說明書圖 4 在光碟機中可控制寫入程序的電路圖         | 268 |

| 圖 24'109 號專利圖 3 本發明之光碟機較佳實施例之流程圖             | 269 |

| 圖 25 '955 號專利說明書圖 1 本發明第一個實施例之光碟機的流程圖        | 270 |

| 圖 26 '552 號專利說明書圖 1 本發明較佳實施例之光碟機,可提供控制系統的流程圖 | 271 |

| 圖 27 '755 號專利說明書圖 4 在光碟機中可控制寫入程序的電路圖         | 272 |

| 圖 28 EP 272 號專利說明書圖 1 光碟紀錄介質相變化介面之剖面圖        | 274 |

| 圖 29 EP 962 號專利說明書圖 1B 較佳之寫入策略脈衝波形圖          | 275 |

| 圖 30 EP 272 號專利說明書圖 1 光碟紀錄介質相變化介面之剖面圖        | 282 |

| 圖 31 EP 962 號專利說明書圖 1B 較佳之寫入策略脈衝波形圖          | 283 |

| 圖 32 '465 號專利說明書圖 2 本專利所揭示之 GSM 系統的邏輯通道介紹示意圖 | 322 |

| 圖 33 '178 號專利說明書圖 2 本專利所揭示之電信系統發射器方塊圖        | 324 |

| 圖 34 '651 號專利說明書圖 4 本專利所揭示之第二個實施例            | 326 |

| 圖 35 '904 號專利說明書圖 3 本專利所揭示之 GSM 系統的收發器方框圖    | 328 |

| 圖 36 '135 號專利說明書圖 2 專利所揭示之 RLC 資料區塊下行示意圖     | 330 |

| 啚 | 圖 37 '548 號專利說明書圖 4A 本專利所揭示之存取探測傳輸與存取探測序列示意圖        | 331  |

|---|-----------------------------------------------------|------|

| 啚 | 圖 38 '727 號專利說明書圖 4A 本專利所揭示之一個加密環境方框圖               | 332  |

| 昌 | 圖 39 '940 號專利說明書圖 4A 本專利所揭示之無線接口的協議架構在用戶設備與結點 B     | 3與圖一 |

|   | 中的無線網路控制器 RNC 之間                                    | 334  |

| 圖 | 圖 40 '672 號專利說明書圖 1 本專利所揭示之實施例之蜂巢狀無線通信系統            | 335  |

| 圖 | 圖 41 '621 號專利說明書圖 6 本專利所揭示之第一個例子之實施方法之流程圖           | 337  |

| 圖 | 圖 42 '213、'333 號專利說明書圖 1(A)1(B): 系爭發明可移動的質量驅動器      | 364  |

| 圖 | 圖 43'213 號、'333 號專利說明書圖 19(B): 系爭發明產生震動運作圖          | 364  |

| 圖 | 圖 44' 333 號專利說明書圖 27:觸覺回饋人機介面裝置的運作圖                 | 365  |

| 啚 | 圖 45 IMMERSION 控告 SONY 系爭產品:DUALSHOCK 遊戲機搖桿和 PS 遊戲機 | 367  |

| 圖 | 圖 46 '273 號專利說明書圖(1):爭發明鍵盤之掃描碼資訊傳遞圖                 | 449  |

| 圖 | 圖 47 '275 號專利說明書圖(1):系爭發明電池充電系統圖                    | 451  |

| 圖 | 圖 48 '100 號專利說明書代表圖(1):記憶體控制模組系統匯流排處理圖              | 453  |

| 圖 | 圖 49 '273 號專利說明書代表圖(5):系爭發明包含附加功能鍵之鍵盤圖              | 454  |

| 圖 | 圖 50 '273 號專利代表圖(1):系爭發明鍵盤掃描碼資訊傳遞圖                  | 455  |

| 啚 | 圖 51 '275 號專利代表圖(1):系爭發明電池充電系統圖                     | 456  |

| 圖 | 圖 52 '100 號專利說明書圖(1):記憶體控制模組系統匯流排處理圖                | 457  |

| 圖 | 圖 53 '100 號專利說明書圖(2A): 系爭專利實施例代表圖                   | 458  |

| 圖 | 圖 54 '275 號專利引證案'361 號專利說明書圖(1):系爭發明電源供應系統圖         | 460  |

| 圖 | 圖 55 '100 號專利引證案'929 號專利說明書圖(1): 系爭發明自 DRAM 讀取資料代表圖 | 462  |

| 圖 | 圖 56 '100 號專利引證案'331 號專利說明書圖(1): 系爭發明技術運用之電腦系統圖     | 465  |

| 圖 | 圖 57 '100 號專利引證案'278 號專利說明書圖(3): 系爭發明之記憶體控制器圖       | 467  |

| 圖 | 圖 58 '100 號專利引證案'536 號專利說明書圖(1)                     | 469  |

| 圖 | 圖 59 '100 號專利引證案'163 號專利說明書圖(1):系爭發明處理器代表圖          | 471  |

| 圖 | 圖 60 義隆電子'352 號專利爭訟歷程                               | 558  |

| 圖 | 圖 61 '352 號專利圖 7B 偵測複數手指與感測板接觸之耦合點,並以之控制游標移動的顯      | 顛示圖  |

|   |                                                     | 561  |

| 圖 | 圖 62 日本專利 JP6161661A 圖 1 本輸入裝置之概略方塊示意圖              | 565  |

| 圖 | 圖 63 '358 號專利圖 8-1 以更廣義的例子將本發明以流程圖顯示指向裝置的高層次算法=     | 之步驟  |

|   |                                                     | 571  |

| 圖 | 圖 64 日本專利 JP6161661A 圖 1 本輸入裝置之概略方塊示意圖              | 588  |

| 圖 | 圖 65 '592 號專利說明書圖 11 依本發明所形成之金屬半導體接面                | 604  |

| 圖 | 圖 66 '830 號專利說明書圖 10 接下來的處理步驟的部分觀察                  | 605  |

| 啚 | 圖 67 '893 號專利說明書圖 4 當工作電壓被供給至 MOS 電晶體時此狀態之結構剖面圖     | 607  |

| 圖 | 圖 68 '990 號專利說明書圖 3A 與 3B 根據本發明之記憶體示意圖              | 609  |

| 圖 | 圖 69 '200 號專利說明書圖 1 說明本發明中重要組成部分的電路安排之電路區塊圖         | 611  |

| 圖 | 圖 70 '434 號專利說明書圖 2 本發明其中一實施例之乘法器電路區塊示意圖            | 613  |

| 圖 | 圖 71 '879 號專利說明書圖 2 說明本發明之處理系統的原理框架圖                | 615  |

| 圖 | 72 '750 號專利說明書圖 2 雙指令集 CPU 的區塊示意圖                     | 617 |

|---|-------------------------------------------------------|-----|

| 圖 | 73 '065 號專利說明書圖 3 本發明之校準和曝光裝置進行校準和曝光過程的控制命令之流         | 程圖。 |

|   |                                                       | 619 |

| 圖 | 74'592 號專利說明書圖 7 依先前技藝形成之金屬與矽接面                       | 620 |

| 圖 | 75 '893 號專利說明書圖 1 本發明之一實施例, MOS 電晶體的結構剖面圖             | 621 |

| 圖 | 76 '893 號專利說明書圖 6 依先前技藝製成之 MOS 電晶體的結構頗面圖              | 622 |

| 圖 | 77 '434 號專利說明書圖 1A 先前技藝的乘法器電路之區塊示意圖                   | 624 |

| 圖 | 78'912 號專利說明書圖本發明使用的沉積室之部分部分橫切面側面圖                    | 627 |

| 圖 | 73 '063 號專利圖 9 本發明之磨擦製程與圖 11 本發明中在一基質上之一間隙子之俯視圖       | 713 |

| 圖 | 74 '006 號專利圖 1 本發明之顯示裝置等尺寸圖                           | 715 |

| 啚 | 75 '556 號專利圖 2 沿 II-II 斷面線之代表圖與圖 8 當鈍化層之蝕刻速率大於閘絕緣層蝕刻  | 速率  |

|   | 時,經鈍化層與閘絕緣層之穿透孔代表圖                                    | 717 |

| 啚 | 76 '674 號專利圖 3 一包含圖 1 和圖 2 特徵產品之電路佈置符號圖解與圖 4 以圖 3 所示產 | 品沿  |

|   | 4-4 線斷面之代表圖                                           | 720 |

| 啚 | 77 '941 號專利圖 2 根據技術之狀態所做出暫時性圖像                        | 722 |

| 啚 | 74 LOWE 引證案圖 1A 及圖 1B 面板之橫截面圖                         | 727 |

| 啚 | 74 MIYAZAKI 引證案圖 12 本發明第七實施例之縱切面圖                     | 729 |

| 啚 | 74 SCHEUBLE 引證案圖 17 顯示一電光學系統中與同質性向列型液晶呈一直線排列之液        | 晶與  |

|   | 雙折射函數相關之傳導特性                                          | 731 |

|   |                                                       |     |

# 第三節 LG v. Quanta

LG Electronics, Inc.

v.

#### Quanta Computer, Inc.

### 1. 前言

本案為韓國電子科技廠商 LG Electronics, Inc. (以下簡稱 LG)和台灣筆記型電腦代工廠廣達電腦 Quanta Computer, Inc. (以下簡稱 Quanta)之間的專利權訴訟。LG 公司已成立超過 50 年,其產品主要為消費性電子產品、行動通訊、以及生活家電用品,不斷致力於提昇品牌的國際知名度之下,LG 已是國際知名的電子產業大廠,其在顯示器、行動裝置等技術上擁有相當多的專利,並多次向競爭對手提起專利訴訟,收取權利金。Quanta 是知名的筆記型電腦研發設計製造公司,亦是全球最大的電腦代工廠,其市佔率超過 25%。此案源起於和 LG 簽署專利授權契約的晶片製造商 Intel 公司,將結合 LG 專利的微處理器與晶片組販售給 Quanta 等電腦製造廠商,Quanta 等製造廠商又將微處理器與晶片組與自己生產的產品相結合,此舉被 LG 認為違反與 Intel 協議的授權規定,因此 LG 便對Quanta 等製造廠商提出專利侵權訴訟。此案經歷一二審後最終上訴至美國聯邦最高法院,主要爭點包含:

- (1) 是否存在默示授權

- (2) 方法專利是否有權利耗盡原則之適用

專利權人在依專利法所賦予之權利進行製造、販售或同意他人製造、販售其專利物品等這些可從中獲取利益之行為後,若能再對該物品主張專利權,將影響該專利物品之流通與利用。為解決此種問題因而發展出權利耗盡原則,以期於專

利權人私權與公共利益之間取得平衡,但長久以來法院並不認同方法專利得適用權利耗盡原則。此案即著重於探討權利耗盡原則之適用,最終 Quanta 在最高法院獲得勝利,結束這場歷經三個審級、長達七年的訴訟戰爭,其判決結果對專利權人、產業鏈之上下游業者以及最終消費者產生相當大的影響。

# 2. 案件基礎資料

#### 2.1 一審

表 25 LG 控告 Quanta 一審案件基礎資料表

| 表 25 LG 控告 Quanta 一番条件基礎資料表 |                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 本案原告                        | LG Electronics, Inc.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 原告訴訟代理人                     | Thomas B. Kenworthy, Scott A. Stempel, Collin W. Park, Morgan Lewis & Bockius LLP, Nathan Wayne McCutcheon, Park, Morgan Lewis & Bockius, Washington, DC, Matthew T. Powers, Sidley Austin Brown & Wood LLP, San Francisco, CA,                                                                                                                                                             |  |  |  |

| 本案被告                        | Asustek Computer, Inc., and Usus Computer International, Inc., Bizcom Electronics, Inc., Compal Electronics, Inc., and Sceptre Technologies, Inc., First International Computer, Inc. and First International Computer of America, Inc., Q-lity Computer, Inc., Quanta Computer, Inc., and Quanta Computer USA, Inc., Everex Systems, Inc.,                                                 |  |  |  |

| 被告訴訟代理人                     | Ronald S. Lemieux, Michael E. Sobel, John V. Komar, Vidya R. Bhakar, Squire Sanders & Dempsey L.L.P., Palo Alto, CA, Quoc-Huy D. Do, Bhakar, Sqire Sanders & Dempsey LLP, San Francisco, CA, John Anson Burlingame, Squire Sanders & Demsey, Washington, DC, James Mason Smith, Squire Sanders & Demsey, Palo Alto, CA, Adam R. Fox, Squire Sanders & Demsey, Los Angeles, CA, Daniel Lewis |  |  |  |

|                   | Hawes, Hawes & Associates, New Baltimore, VA, John   |  |  |  |  |

|-------------------|------------------------------------------------------|--|--|--|--|

|                   | Anson Burlingame, Squire Sanders & Dempsey,          |  |  |  |  |

|                   | Washington, DC, James Mason Smith, Squire Sanders &  |  |  |  |  |

|                   | Dempsey, Palo Alto, CA, David Morris, Morgan Lweis & |  |  |  |  |

|                   | Bockius LLP, Washington, DC                          |  |  |  |  |

| 技術領域              | 資料處理系統及其中的運行方法各方面的數項專利                               |  |  |  |  |

| 系爭產品              | Intel 微處理器 (microprocessor)、晶片組 (chipsets)           |  |  |  |  |

|                   | U.S. Pat 4,918,645 ('645 patent);                    |  |  |  |  |

|                   | U.S. Pat 4,939,641 ('641 patent);                    |  |  |  |  |

| <br>  系爭專利        | U.S. Pat 4,926,419 ('419 patent);                    |  |  |  |  |

| がす <del>ず</del> が | U.S. Pat 5,077,733 ('733 patent);                    |  |  |  |  |

|                   | U.S. Pat 5,379,379 ('379 patent);                    |  |  |  |  |

|                   | U.S. Pat 5,892,509 ('509 patent).                    |  |  |  |  |

| 起訴法院              | 加州北區聯邦地方法院(United States District Court, N.D.        |  |  |  |  |

| California )      |                                                      |  |  |  |  |

| 起訴日期              | 2001年4月16日                                           |  |  |  |  |

| <i>协</i> 4上 口 Hu  | 2003 年 2 月 06 日即決判決認為 LG 系統裝置專利已耗                    |  |  |  |  |

| 終結日期              | 盡,但方法專利未被耗盡。                                         |  |  |  |  |

| 引用文獻              | 申請專利範圍解釋: 2002 WL 34477708                           |  |  |  |  |

| 是否上訴二審            | 是                                                    |  |  |  |  |

# 2.2 二審

表 26 LG 控告 Quanta 二審案件基礎資料表

| 本案原告上訴人  | LG Electronics, Inc.                                                                                                                                                 |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 原告訴訟代理人  | Richard G. Taranto, Farr & Taranto, of Washington, DC, argued for plaintiff-appellant.  On the brief was Michael J. Schaengold, Patton Boggs LLP, of Washington, DC. |  |  |

| 本案被告被上訴人 | Bizcom Electronics, Inc., Compal Electronics, Inc., and Sceptre Technologies, Inc., Defendants-Cross Appellants, Everex Systems, Inc., Defendant-Appellee,           |  |  |

|               | First International Computer Inc. and First International Computer of America, Inc., Defendants-Cross Appellants, |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------|--|--|

|               | Q-Lity Computer, Inc., Quanta Computer, Inc., and Quanta                                                          |  |  |

|               | Computer USA, Inc., Defendants-Cross Appellants.                                                                  |  |  |

|               | William J. Anthony, Jr., Orrick, Herrington & Sutcliffe LLP,                                                      |  |  |

|               | of Menlo Park, California, argued for defendants-cross                                                            |  |  |

|               | appellants Bizcom Electronics, Inc., et al. With him on the                                                       |  |  |

|               | brief were Eric L. Wesenberg, Kaiwen Tseng, Matthew J.                                                            |  |  |

|               | Hult and Rowena Y. Young.                                                                                         |  |  |

|               | Joseph L. Strabala, Law offices of Joseph L. Strabala, of San                                                     |  |  |

|               | Francisco, California for defendant-appellee Everex                                                               |  |  |

|               | Systems, Inc., joined in the co-defendants' briefs.                                                               |  |  |

|               | Ronald S. Lemieux, Paul, Hastings, Janofsky & Walker LLP,                                                         |  |  |

| 被告訴訟代理人       | of Palo Alto, California for defendants-cross appellants First                                                    |  |  |

|               | International Computer, Inc., et al. Of counsel on the brief                                                      |  |  |

|               | was James M. Smith, Squire, Sanders & Dempsey L.L.P., of                                                          |  |  |

|               | Palo Alto, California.                                                                                            |  |  |

|               | Terry D. Garnett, Paul, Hastings, Janofsky & Walker LLP, of                                                       |  |  |

|               | Los Angeles, California for defendants-cross appellants                                                           |  |  |

|               | Q-Lity Computer, Inc., et al. With him on the brief were                                                          |  |  |

|               | Vinent K. Yip, Maxwell A. Fox, Peter J. Wied, Sang N.                                                             |  |  |

|               | Dang and Jay C. Chiu. Of counsel was Jeffrey D. Mills,                                                            |  |  |

|               | Fulbright & Jaworski L.L.P., of Austin, Texas.                                                                    |  |  |

| 技術領域          | 資料處理系統及其中的運行方法各方面的數項專利                                                                                            |  |  |

| 系爭產品          | Intel 微處理器(microprocessor)、晶片組(chipsets)                                                                          |  |  |

|               | U.S. Pat 4,918,645 ('645 patent);                                                                                 |  |  |

|               | U.S. Pat 5,077,733 ('733 patent);                                                                                 |  |  |

| 系爭專利          | U.S. Pat 4,939,641 ('641 patent);                                                                                 |  |  |

|               | U.S. Pat 5,379,379 ('379 patent);                                                                                 |  |  |

|               | U.S. Pat 5,892,509 ('509 patent).                                                                                 |  |  |

| 起訴法院          | 聯邦巡迴上訴法院(United States Court of Appeals, Federal                                                                  |  |  |

| Z W I I A I I | Circuit.)                                                                                                         |  |  |

| 起訴日期          | 2005年3月24日                                                                                                        |  |  |

| 終結日期          | 2006年7月07日維持默示授權不存在及權利耗盡原則不                                                                                       |  |  |

| 心而日朔          | 適用方法專利之認定,另外推翻系爭系統專利已耗盡之決                                                                                         |  |  |

|      | 定,認為專利權耗盡不適用於附條件之販售。 |  |  |  |

|------|----------------------|--|--|--|

| 引用文獻 |                      |  |  |  |

| 是否上訴 | 是                    |  |  |  |

# 2.3 三審

表 27 LG 控告 Quanta 三審案件基礎資料表

| 表 27 LG 控告 Quanta 三番案件基礎資料表 |                                                                                                                                                                                                                                                                                                                                           |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 本案上訴人                       | Quanta Computer, Inc., et al                                                                                                                                                                                                                                                                                                              |  |  |

| 上訴訴訟代理人                     | Terrence D. Garnett, Vincent K. Yip, Peter Wied, Paul, Hastings, Janofsky & Walker LLP, Los Angeles, CA, Maureen E. Mahoney, Counsel of Record, J. Scott Ballenger, Barry J. Blonien, Melissa B. Arbus, Anne W. Robinson, Latham & Watkins LLP, Washington, D.C., Maxwell A. Fox, Paul, Hastings, Janofsky & Walker LLP, Minato–Ku, Tokyo |  |  |

| 本案被上訴人                      | LG Electronics, Inc.                                                                                                                                                                                                                                                                                                                      |  |  |

| 被上訴訴訟代理人                    | Carter G. Phillips, Counsel of Record, Virginia A. Seitz,<br>Jeffrey T. Green, Jeffrey P. Kushan, Rachel H. Townsend,<br>Quin M. Sorenson, Sidley Austin LLP, Washington, D.C.                                                                                                                                                            |  |  |

| 技術領域                        | 資料處理系統及其中的運行方法各方面的數項專利                                                                                                                                                                                                                                                                                                                    |  |  |

| 系爭產品                        | Intel 微處理器(microprocessor)、晶片組(chipsets)                                                                                                                                                                                                                                                                                                  |  |  |

| 系爭專利                        | U.S. Pat 4,939,641 ('641) ('641 patent);<br>U.S. Pat 5,379,379 ('379) ('379 patent);<br>U.S. Pat 5,077,733 ('733) ('733 patent)                                                                                                                                                                                                           |  |  |

| 起訴法院                        | 美國聯邦最高法院(Supreme Court of the United States)                                                                                                                                                                                                                                                                                              |  |  |

| 起訴日期                        | 2007年3月09日                                                                                                                                                                                                                                                                                                                                |  |  |

| 終結日期                        | 2008 年 6 月 09 日判定當方法專利能體現於一物體之上時,販賣此物品即造成專利權的耗盡,因此 LG 專利權利已耗盡無法主張侵權。                                                                                                                                                                                                                                                                      |  |  |

| 引用文獻                        |                                                                                                                                                                                                                                                                                                                                           |  |  |

| 是否上訴 | 不適用 |

|------|-----|

|------|-----|

### 3. 案件简介

### 3.1 本案事實

原告LG擁有與電腦系統處理器之訊息讀寫排程相關的系統與方法專利,為解決LG與Intel間長久的專利權爭議,兩家公司進行專利和解並簽訂授權契約,LG將其與資料讀寫處理有關的專利組合授權給Intel,讓Intel得製造及販售實施有LG專利之微處理器(Microprocessor)與晶片組(Chipsets)(以下簡稱Intel產品)。LG為試圖避免第三人因默示授權而將自Intel購得之Intel產品與其他零件組合使用並實施專利發明進而完成電腦系統,因此同時在授權契約之外的主契約(Master Agreement)中提及授權契約中雙方約定不論基於明示或默示之授權,LG給予Intel之授權不包括給予電腦系統製造商結合使用Intel產品與非Intel生產的產品之權利,並要求Intel需書面通知其客戶<sup>7</sup>(但契約中也表明該契約不改變權利耗盡原則之適用<sup>8</sup>)。利用這些契約,LG欲施加售後使用限制約款使Intel之銷售為一附條件販賣,希望能排除方法專利上權利耗盡的適用。

而 Quanta 等電腦製造廠向 Intel 購買該系爭產品,Intel 按照與 LG 契約之規定,以信件通知客戶關於不得將 Intel 產品與非 Intel 生產之產品結合使用之售後限制,但 Quanta 等電腦廠商仍將該 Intel 產品與其他廠牌製造之記憶體與匯流排等零件組裝成電腦產品後販售,因而被 LG 控告專利侵權。Quanta 主張 LG 之專利在 Intel 有權販賣下已發生權利耗盡,LG 則主張方法專利不適用權利耗盡原則,且 Intel 之販售違反授權契約為無權販售亦不存在默示授權。本案的主要爭點有以下兩者,一、是否存在默示授權;二、方法發明專利是否有權利耗盡原則之適用。

<sup>&</sup>lt;sup>7</sup> Quanta Computer, Inc. v. LG Elecs., Inc., 553 U.S. 617, 2110 (2008).

<sup>&</sup>lt;sup>8</sup> *Id.* at 2114.

#### 3.2 兩造背景

LG 創立於 1958,至今已成立超過 50 年,公司員工超過 8 萬 4 千人,在全球擁有 112 個服務營運據點(包括 81 家子公司)。2008 年,LG 全球銷售額達 447 億美元,其產品主要為消費性電子產品、行動通訊、以及生活家電用品,旗下有五大事業體:家庭娛樂、行動通訊、生活家電、冷氣空調以及企業解決方案。不斷致力於提昇品牌的國際知名度之下,LG 已是國際知名的電子產業大廠,其在顯示器、行動裝置等技術上擁有相當多的專利,並多次向競爭對手提起專利訴訟收取權利金。

Quanta 成立於 1988 年,是知名的行動裝置研發設計製造公司,抑是全球最大的電腦代工廠,其市佔率超過 25%,全球的員工已逾七萬人,台灣營運總部約有 5,000 名員工,多半是研發及工程人員。其代工許多品牌之硬體設備,例如Acer、IBM、HP、戴爾、Apple 電腦、Toshiba、Sony、Lenovo等。但由於產品眾多,也使 Quanta 時常成為專利訴訟攻擊的對象,Quanta 最近才於 2011 年 10月與微軟(Microsoft)達成和解,Quanta 必須支付專利授權費用給微軟公司。

### 3.3 本案主要程序進行時程

表 28 LG 控告 Quanta 主要程序進行時程表

| 程序名稱                                         | 時間點        | 程序結論                                                   |

|----------------------------------------------|------------|--------------------------------------------------------|

| LG一審起訴                                       | 2001年4月16日 |                                                        |

| 專利範圍解釋(2002<br>WL 34477708)                  | 2002年8月20日 | 針對美國<br>第'645、'641、'419、'733、'379、'509<br>號專利之申請專利範圍解釋 |

| 聯邦地方法院針對是<br>否准許即決判決討論<br>(2002 WL 31996860) | 2002年8月20日 | 准許 Quanta 即決判決之申請                                      |

| 一審聯邦地方法院即                                    | 2003年2月06日 | LG 因專利權利耗盡而無法對                                         |

| 決判決(248 F.Aupp.2d             |            | Quanta 主張專利侵權。                    |

|-------------------------------|------------|-----------------------------------|

| 912)                          |            | 方法專利之侵權不因默示授權或權                   |

|                               |            | 利耗盡而無法主張。                         |

| 二審聯邦巡迴上訴法<br>院(452 F.3d 1364) | 2006年7月7日  | 部分維持部分改判聯邦地方法院判<br>決,認為LG得主張其專利權。 |

| 三審聯邦最高法院<br>(553 U.S.617)     | 2008年6月09日 | 系爭專利權利耗盡,LG無法主張其<br>專利權           |

# 3.4 本案系爭專利、系爭產品技術內容

### 3.4.1 本案系爭專利

# (1) 美國第 4,939,641 號專利

| USPC 分類<br>號 | 364/200, 364/243.4,<br>364/243.41, 364/259.2                      | 申請號   | 07/213556                                                         |

|--------------|-------------------------------------------------------------------|-------|-------------------------------------------------------------------|

| IPC 分類號      | G06E 013/00                                                       | 專利名稱  | 有快取記憶體的多工系<br>統(Multi-Processor<br>System With Cache<br>Memories) |

| 專利號          | 4,939,641                                                         | 專利權人  | Wang Laboratories, Inc.,<br>Lowell, MA                            |

| 發明人          | Schwartz, Martin J., Worcester, MA Becker, Robert D., Shirley, MA | 早期公開日 | 無                                                                 |

| 申請日          | 1988-06-30                                                        | 公開日   | 1990-07-03                                                        |

| 優先權日         | 1988-06-30                                                        | 優先權案號 | US1988213556A                                                     |

| 專利摘要         | 一種在 CPU 中描述的系統,包含主記憶體及匯流排等裝置。快取記憶體負責組合 CPU 和匯流排以提供其內儲存的數據單元狀      |       |                                                                   |

况之指示。一個指示的訊號告知該內容的儲存位置是否被變更, 因為那些內容是從主記憶體接收而儲存位置的目錄可能是在別 處。控制器的功能是用來確認當接收到來自 CPU 的資料單元且 將之儲存於與 CPU 相連的快取記憶體中時,該資料單元同時被 儲存於與另一 CPU 相連的快取記憶體中,此資料單元也會被寫 入主記憶體中。在過程中,其他的快取記憶體監控匯排流並持續 更新相關的資料。匯排流監視器監視所有寫入到主記憶體以及從 主記憶體中讀出的資料,確保整個系統數據的完整性。 技術特徵 避免使用合法/不合法的判斷位元及降低存取主記憶體的次數。 此系統包含一個 CPU (10)、一個主記憶體(14)、一個快取 記憶體、及一個連接兩記憶體的匯流排(42)。快取包含有資料 的現狀,其中一指示從主記憶體接收後其儲存的位置是否被修 改,另一指示是否有相同的內容儲存在其他記憶體中。快取控制 功效說明 器(40)(Cache Controller)若資料從一CPU中被寫入他的快 閃位置時有另一相對的快閃位置,則將此資料寫入主記憶體中。 每個快取監控器讀取並寫入往返於主記憶體的資料並隨時更新 拷貝相關的資料。 代表圖 圖 14'641 號專利說代表圖專利發明之高階方塊圖 10:中央處理器 (Central Processing Unit) 元件符號說 12:中央處理器 (Central Processing Unit)

明 14: 主記憶體 (Main Memory)

16: 位址轉譯器 (Address Translator)

16': 位址轉譯器 (Address Translator)

18: 多工器 (Multiplexer)

18': 多工器 (Multiplexer)

20:實體位址暫存器 (Physical Address Register)

20':實體位址暫存器 (Physical Address Register)

22: 數位線 (Cable)

22': 數位線 (Cable)

24: 快取匯流排 (Cache Bus)

24': 快取匯流排 (Cache Bus)

26: 快取資料匯流排 (Cache Data Bus)

26': 快取資料匯流排 (Cache Data Bus)

27: 數位線 (Cable)

27': 數位線 (Cable)

28:快取標籤儲存區 (Cache Tag Store)

28': 快取標籤儲存區 (Cache Tag Store)

30: 重複位元暫存器 (Dirty Bit Register)

30': 重複位元暫存器 (Dirty Bit Register)

32:分享位元暫存器 (Shared Bit Register)

32': 分享位元暫存器 (Shared Bit Register)

34: 數位線 (Cable)

34': 數位線 (Cable)

36:比較器 (Comparator)

36': 比較器 (Comparator)

38: 數位線 (Cable)

38': 數位線 (Cable)

39: 線 (Line)

40: 快取控制器 (Cache Controller)

40': 快取控制器 (Cache Controller)

42: 數位線 (Cable)

42': 數位線 (Cable)

43: 線 (Line)

43': 線(Line)

44:數位線 (Cable)

44': 數位線 (Cable)

45: 線 (Line)

45': 線 (Line)

第二章 第三節 LG v. Quanta 49: 數位線 (Cable) 49': 數位線 (Cable) 50: 資料匯流排介面(Data Bus Interface) 50':資料匯流排介面(Data Bus Interface) 51: 數位線 (Cable) 52: 位址匯流排介面(Address Bus Interface) 52':位址匯流排介面(Address Bus Interface) 53: 主控制線 (Main Control Line) 54:控制單元 (Control Unit) 55:分享線 (Shared Line) 56: 數位線 (Cable) 56': 數位線 (Cable) 57:停止線 (Hold Line) 57': 停止線 (Hold Line) 58:外部位址暫存器 (External Address Register) 58': 外部位址暫存器 (External Address Register) 59: 匯流排鎖定線(Bus Lock Line) 60: 線 (Line) 60': 線 (Line) 61: 輸出出入介面 (I/O Interface) 62: 數位線 (Cable) 62': 數位線 (Cable) 63: 系統控制介面單元 (System Control Interface Unit) 64:比較器 (Comparator) 64': 比較器 (Comparator) 66: 數位線 (Cable) 66': 數位線 (Cable) 67: 線 (Line) 67': 線 (Line) 68: 數位線 (Cable) 68': 數位線 (Cable) 70: 線 (Line) 70':線 (Line) 72: 線 (Line) 72': 線 (Line)

90: 多字傳輸暫存器 (Multi Word Transfer Register)

80: 數位線 (Cable) 80': 數位線 (Cable) 90':多字傳輸暫存器 (Multi Word Transfer Register)

102:資料匯流排 (Data Bus) 104:位址匯流排 (Address Bus) 106:控制匯流排 (Control Bus)

### (2) 美國第5,379,379 號專利

| USPC 分類<br>號 | 395/250, 395/425,<br>395/725, 364/239.5,<br>364/242.91, 364/246.6,<br>364/DIG. 1, 364/937.01,<br>364/939.1, 364/969,<br>364/DIG. 2       | 申請號   | 07/580365                                                                                                     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------|

| IPC 分類號      | G06F 013/16                                                                                                                              | 專利名稱  | 有選擇排成讀寫處理的記憶體控制單元(Memory<br>Control Unit With<br>Selective Execution Of<br>Queued Read And Write<br>Requests) |

| 專利號          | 5,379,379                                                                                                                                | 專利權人  | Wang Laboratories, Inc.,<br>Lowell, MA                                                                        |

| 發明人          | Becker, Robert D., Shirley, MA Schwartz, Martin J., Worcester, MA Curcuru, Kevin H., Pepperell, MA Eng, Kenneth J., West Bridgewater, MA | 早期公開日 | 無                                                                                                             |

| 申請日          | 1990-09-06                                                                                                                               | 公開日   | 1995-01-03                                                                                                    |

| 優先權日         | 1988-06-30/1990-09-06                                                                                                                    | 優先權案  | US1988213395A/                                                                                                |

|      |                                                                                                                                                     | 號                                                                                                                                                                         | US1990580365A                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 專利摘要 | 個或多個記憶單元(Mem<br>排(System Bus),其中<br>的系資料匯流排(Syster<br>的人及包含<br>的人人會用。<br>一个<br>一个<br>一个<br>一个<br>一个<br>一个<br>一个<br>一个<br>一个<br>一个<br>一个<br>一个<br>一个 | ory Units)的<br>包括 Bus)的<br>System Addr<br>(System Addr<br>)<br>(System Addr<br>)<br>(System Addr<br>)<br>(新)<br>(新)<br>(新)<br>(新)<br>(新)<br>(新)<br>(新)<br>(新)<br>(新)<br>( | Unit,MCU)包括連結一<br>內第一介面、連結系統匯流<br>以單元(Information Units)<br>以單元(Information Units)<br>以電體讀取及寫入。MCU<br>以電體讀取及介面。MCU<br>以要求的與解,一個記憶理,可<br>以與不可將是<br>以與不可,個記憶理,<br>以與不可,因之以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以與不可,<br>以<br>以<br>以<br>的<br>的<br>的<br>的<br>的<br>的<br>的<br>的<br>的<br>的<br>的<br>的<br>的<br>的<br>的<br>的 |

| 技術特徵 | 使中央記憶體系統連接到的速率同時確保正確的讀.                                                                                                                             |                                                                                                                                                                           | <b>連的系統匯流排。保持存取</b><br>5。                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 功效說明 | 32)及系統匯流排(SBI<br>MCU(22)。通常所有來<br>MCU中排隊,且讓讀取要<br>輯可比較每個讀取和寫入<br>在排隊中的寫入要求有相                                                                        | 2)。所有的<br>农自系統匯流<br>要求優先於寫<br>要求,若一個<br>關,則處理在                                                                                                                            | 这多個記憶單元(26,28,30,<br>讀取及寫入要求被緩衝至<br>排的讀取和寫入要求都在<br>入要求。MCU 同時包含邏<br>固讀取要求所要求的位址與<br>在該寫入要求前的所有讀取<br>立址的讀取要求之前,先處                                                                                                                                                                                                                                                                                                                              |

### (3) 美國第5,077,733 號專利

| USPC 分類<br>號 | 370/085.6, 370/085.11,<br>340/825.5                                                                                                                                                                                                                                                       | 申請號   | 07/405792                                                                                                |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------|

| IPC 分類號      | H04L 005/22                                                                                                                                                                                                                                                                               | 專利名稱  | 可排定的停留節點的排程<br>裝置(Priority Apparatus<br>Having Programmable<br>Node Dwell Time)                          |

| 專利號          | 5,077,733                                                                                                                                                                                                                                                                                 | 專利權人  | Wang Laboratories, Inc.,<br>Lowell, MA                                                                   |

| 發明人          | Whipple, David L., Braintree, MA                                                                                                                                                                                                                                                          | 早期公開日 | 無                                                                                                        |

| 申請日          | 1989-09-11                                                                                                                                                                                                                                                                                | 公開日   | 1991-12-31 *Notice: The portion of the term of this patent subsequent to 2007/05/15 has been disclaimed. |

| 優先權日         | 1989-02-28/1989-09-11                                                                                                                                                                                                                                                                     | 優先權案號 | US1989317100A/US1989<br>405792A                                                                          |

| 專利摘要         | 一種裝置用來決定一組要使用匯流排的節點(Node)去使用匯流排的優先順序(Priority),為了決定這個優先順序,這個裝置將這些節點環狀排列並選擇其中一節點當參考節點(Anchor Node),此參考節點有最高的順位,而其他節點的優先順序由其位置與參考節點位置的距離做決定。每個節點包含一個預先設定的計數器(Counter)用來指出一個節點在最優先的順位移轉給其他節點前能使用匯流排資源的時間,當其中一個節點使用匯流排的次數到達預先決定的存取次數時,目前的參考節點將不再是參考節點而由下一個環狀上的節點當做新的參考節點,其他節點的優先順序因更換參考節點而改變。 |       |                                                                                                          |

| 技術特徴       | 透過排程單元間的優先順序,使兩個單元輪流享有對該匯流排的優先存取次序,且高使用量的元件具有較高的循環次數,使匯排流不會無止盡的被其中一單元霸佔。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 功效說明       | 此裝置包含一組連結在匯流排上的端點(Peripheral)或節點。每個節點都接收到來自相鄰節點的一個優先順序,並提供另一優先順序給下一個環狀上相鄰的節點。邏輯判斷當沒有其他更高順位的節點要求存取時讓此節點存取匯流排。第一順位在一預定存取次數後會交給下一個節點。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 代表圖        | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 元件符號<br>說明 | 108 MEM <sub>1</sub> :第一記憶體單元(Memory Units) 108 MEM <sub>2</sub> :第二記憶體單元(Memory Units) 108 MEM <sub>n</sub> :第 n 記憶體單元(Memory Units) 108 MEM <sub>n+1</sub> :第 n+1 記憶體單元(Memory Units) 108 MEM <sub>n+2</sub> :第 n+2 記憶體單元(Memory Units) 110 CPU <sub>1</sub> :第一中央處理單元(Central Processing Units) 110 CPU <sub>2</sub> :第二中央處理單元(Central Processing Units) 110 CPU <sub>n</sub> :第 n 中央處理單元(Central Processing Units) 110 CPU <sub>n+1</sub> :第 n+1 中央處理單元(Central Processing Units) 112 LSC:本地系統控制器(Local System Controllers) 114 RSC:遠端系統控制器(Remote System Controllers) 116 SBI <sub>1</sub> :第一系統匯流排介面(System Bus Interfaces) 116 SBI <sub>n</sub> :第 n 系統匯流排介面(System Bus Interfaces) |  |

116 SBI<sub>n+1</sub>: 第 n+1 系統匯流排介面 (System Bus Interfaces)

118 SPU: 通訊處理單元 (Satellite Processing Units)

120 SPU BUS: 通訊處理單元匯流排 (Satellite Processing Units

Bus)

#### 3.4.2 專利技術簡介

#### (1) 美國 4,939,641 號專利

電腦系統的主要功能即是透過微處理器(Microprocessor)及中央處理單元 (Central Processing Unit)來解讀程式指令、處理資料、以及控制系統中的裝置。 用金屬線(Wires)或匯排流(Bus)與微處理器組合成為晶片(Chipset)後,即 可透過晶片在裝置與微處理器之間傳遞資訊,這些裝置包括滑鼠、鍵盤、硬碟、 記憶體等。

電腦處理中的資訊通常儲存於隨機存取記憶體之中(Random Access Memory),也是通稱的主記憶體(Main Memory)。而最近期讀取的資料則儲存於位於微處理器上的快取記憶體(Cache Memory),以提供比主記憶體更快速的讀寫功能。

但當複製的資料同時儲存於快取記憶體及主記憶體中,而一邊資料發生更動但另一邊資料仍為更改前版本時則會發生問題,例如,快取記憶體已更新,而主記憶體仍保持其原有資料而未被更新,如此會造成取得資料上的問題。而此'641號專利即負責解決這樣的問題,透過監控被要求的資料並在發現被要求的資料為陳舊的版本時從快取記憶體更新主記憶體中陳舊的資料,以確保系統讀取的都是最新的資料,使系統免於讀取到未儲存的舊版本資訊。

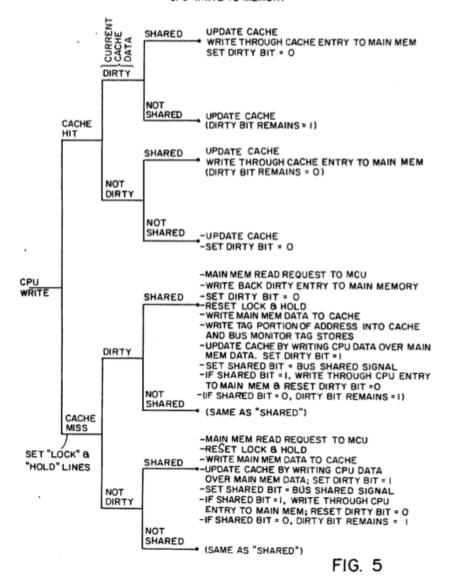

#### CPU WRITE TO MEMORY

圖 17 '641 號專利說明書圖 5 當 CPU 寫入資料到記憶體時的決策樹

#### (2) 美國 5,379,379 號專利

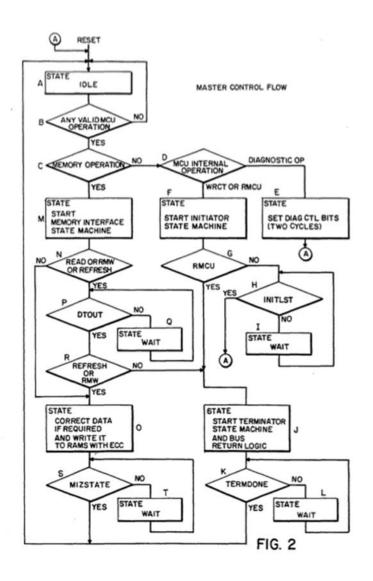

讀取/寫入要求(Request)是當匯流排上的裝置需要從主記憶體讀取/寫入資料時傳遞的要求,此號專利說明如何控制這些需要讀取/寫入主記憶體的要求的順序,考量到電腦在執行讀取要求比執行寫入要求快速,但若所要讀取的資料是在更新的資料寫入之前就被讀取,則此時所讀取的資料反而是舊的資料,因此主要原則為先執行讀取要求,當要讀取的資料經過修改尚未儲存時再處理寫入

#### 的要求。

圖 18 '379 號專利說明書圖 2 表達 MCU 的主控制流程之流程圖

在此專利中,讀寫要求會經過記憶體控制器(Memory Controller)到達主記憶體,記憶體控制器內有讀取/寫入的緩衝區(Buffers),用來暫存準備要傳送給主記憶體的讀寫要求。記憶體控制器理會檢查所有進來的讀取要求所標示的記憶體位址(Memory Address),並將之與緩衝區內的寫入要求標示的記憶體位製作比對,若無相同(Match)的則執行該讀取要求,若出現相同則傳輸該寫入的要求讓記憶體執行寫入的動作,如此就能保證不會讀取到已修改但尚未寫入的舊資料。

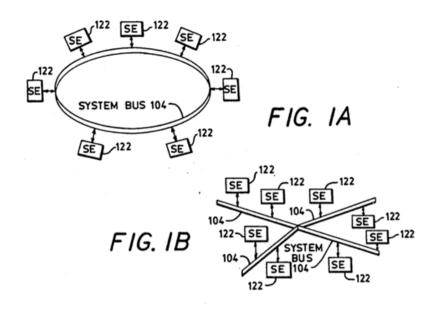

#### (3) 美國 5,077,733 號專利

在匯流排傳輸技術上必須要避免單一組件壟斷匯流排之傳輸功能,且要容許多個元件共享該匯流排,並給予高使用量的元件較高的存取用量。此號專利能解決連接兩電腦單元的匯排流上發生的資訊壅塞情形,他使兩個單元能共用一個匯排流,讓匯排流不被其中一個單元獨佔。此專利揭露一個輪流取得優先存取次序的方法,讓使用中的元件持續使用,直到計數器達到預定的循環次數時換其他單元使用,透過排程單元間的優先順序,使單元輪流享有對該匯流排的優先存取次序,且高使用量的元件具有較高的循環次數,使匯排流不會無止盡的被其中一單元霸佔(Hogging)。

圖 19 '733 號專利說明書圖 1A、1B 拓撲結構之環狀排列的系統匯流排示意圖

#### 3.4.3 被控侵權產品

本案之被控侵權產品為 Intel 生產包含 LG 數項專利的微處理器 (microprocessor) 及晶片組 (chipsets)。

# 4. 案件分析

# 4.1 申請專利範圍解釋 9 (於最高法院爭訟之三項專利)

#### 4.1.1 本案事實

法院已於訴訟程序中,做出申請專利範圍解釋。該三項專利之技術內容依請 求項之描述分析如下:

#### 系爭專利請求項整理表

# (1) 美國 4,939,641 號專利請求項 第1項

1. A data processing system including one or more central processing units, main memory means, and bus means, for each central processing unit the invention comprising: cache memory means coupled between the central processing unit and said bus means; bus monitor means associated with said cache memory means and coupled to said bus means for detecting on said bus means an address associated with a data unit transferred from said main memory means to a bus connection requesting the data unit; means coupled to said cache memory means and to said bus means for determining if data having the same address as said transferred data unit is present in said cache memory means and, if present, for asserting a hold signal on said bus means, the assertion of the hold signal indicating at least to the bus connection requesting the data unit that another data unit may be transmitted over said bus means; and means for detecting whether data corresponding to the address of said transferred data unit and determined to be stored in said cache memory means may be different in content from said transferred data unit and, if so, transmitting said data from said cache memory means to said bus means for reception by the bus connection requesting the data unit.

$<sup>^9</sup>$  LG Electronics, Inc. v. Asustek Computer, Inc., et al., 2002 WL 34477708 (N.D. Cal. Aug. 20, 2002) (markman order).

1. 一種資料處理系統包含一個或多個中央處理器(CPU)、主記憶體裝置(Memory Means)、以及匯流排裝置(Bus Means),每一個 CPU 包含:

在 CPU 以及匯流排之間的快取記憶體裝置 (Cache Memory)、與快取記憶體及匯流排相連的匯流排監視器裝置 (Bus Monitor),用來偵測經由匯流排由主記憶體傳輸至其他要求資料的裝置的資料單元的位址 (Address),若正要傳輸的資料單元位址和快取記憶中儲存的資料有相同時,會以一停止訊號 (Hold Signal) 通知要求該資料的裝置有其他相同位址的資料在快取記憶體中,當正要傳輸的資料與快取記憶體中儲存的資料內容不相同時,則傳輸快取記憶體中的資料給要求資料的裝置。

### (2) 美國 4,939,641 號專利請求項 第5項

5. A data processing system including at least first and second central processing units, main memory means, and bus means, the invention comprising: at least first and second cache memory means respectively coupled between said first and second central processing units and said bus means; bus monitor means associated with each said cache memory means respectively and coupled to said bus means for detecting on said bus means an address associated with a data unit being read from said main memory means; means coupled to said associated cache memory means and to said bus means for determining if said corresponding to said address as detected by said bus monitor means is present in the associated cache memory means and, if said data is found to be present, for asserting a first hold signal on said bus means, the assertion of the first hold signal indicating at least to a bus connection reading the data unit that another data unit may be transmitted over said bus means; and means for detecting whether the data corresponding to said address and stored in said associated cache memory means may be different in content from that detected as being read and, if the data is determined to possibly be different in content, transmitting said data from said associated cache memory means to the bus connection reading the data unit from said main memory.

5.一種資料處理系統(Data Processing System)包含至少第一和第二個 CPU、主記憶體、以及匯流排,專利發明包括:

至少第一和第二個快取記憶體組合於第一和 第二個 CPU 及匯流排之間;

匯流排監視器 (Bus Monitor) 與快取記憶體相連並與匯流排組合,用來偵測在匯流排上從主記憶體中讀取出的資料單元位址;

組合快取記憶體及匯流排的組合,用來決定存在於相連的快取記憶體中偵測匯流排監控器得到相關的位址,若有找到資料,匯流排匯出現第一個停止訊號(Hold Signal),停止訊號指出當一個匯流排上有資料單元在傳輸的過程中,有至少另一資料單元也要使用匯流排資源;

偵測資料的位址與已存於快取記憶體中的資料是否在內容上有不同,若認為內容有不同的可能,從快取記憶體傳送讀取自主記憶體的資料給匯流排。

## (3) 美國 4,939,641 號專利請求項 第14項

14. In a data processing system comprising at least one central processing unit having a cache memory coupled to a system memory through a system bus, the system bus including signal lines for conveying, during bus cycles, address information and data units associated with addresses between the system memory and other bus connections coupled to the system bus, the cache memory comprising: means for monitoring bus transactions occurring on the system bus for determining if a bus transaction occurring during a current bus cycle is an operation initiated by another bus connection that reads one or more data units from an address of the system memory; means for detecting if the address is

associated with one or more data units already stored within the cache memory; and means having an input coupled to said detecting means and responsive thereto and further having an output coupled to the system bus for asserting thereon during the current bus cycle a HOLD signal line, the assertion of the HOLD signal line indicating to the bus connection initiating the read operation that at least one of the data units associated with the address is stored within the cache memory and that the cache memory will, if the data unit is determined to be marked as dirty within the cache memory, transmit the stored data unit to the bus connection during a subsequent bus cycle.

14. 在一個資料處理系統中包含至少一個 CPU 並透過匯流排連結快取記憶體和系統記憶體,系統匯流排包含訊號線用來在匯流排迴圈中傳遞於系統記憶體與匯流排之間的位址資訊以及資料單元,快取記憶體包含:

監控系統匯流排上匯流排之間傳遞的裝置, 監視如果發生在目前匯流排循環期間的匯流 處理,是由另一匯流排從一個系統記憶體的 位址中讀取一個或多個資料單元;

值測位址是否與一或多個已存在於快取記憶 體中的資料單元相關;

對進來的資料進行偵測,停止訊號線(Hold Signal Line)偵測並反應當匯流排連接的讀取運算出現至少一個與此位址相關的資料單元已儲存於快取記憶體中,且該資料單元被標記陳舊資料(Dirty)時,該快取記憶體會傳送該被儲存的資料單元給匯流排。

## (4) 美國 5,379,379 號專利請求項 第1項

1. A memory control unit for controlling a main system memory of a data processing system, the main system memory being comprised of at least one memory unit, comprising: first interface means for coupling said memory control unit to the at least one memory unit of the main system memory; second interface means for coupling said memory

control unit to a system bus having signal lines for expressing information units, including memory read and write requests, the system bus including a system address bus; means, coupled to said first and to said second interface means and responsive to a write request from said system bus, for executing the write request by storing one or more information units within a memory unit at an address specified by the system address bus, said write request executing means comprising write request receiving and buffer means having a plurality of storage locations capable of storing a plurality of received write requests and associated write addresses prior to execution of the write requests; means, coupled to said first and to said second interface means and responsive to a read request from said system bus, for executing the read request by reading one or more information units from a memory unit at a location specified by the system address bus, said read request executing means comprising read request receiving and buffer means having a plurality of storage locations capable of storing a plurality of received read requests and associated read addresses prior to execution of the read control unit requests; said memory further comprising: means, having a first input coupled to said write buffer means and a second input coupled to said read request receiving means, for comparing a received read address to write addresses stored in said write address buffer means, said comparing means having an output signal for indicating, when asserted, an occurrence of the reception of a read address within a predetermined range of addresses of one of said stored write addresses; and means for controlling the execution of read and write requests, said controlling means being coupled to said comparing means output signal and being responsive to said comparing means output signal

not being asserted for causing an execution of all buffered read requests before any buffered write requests, said controlling means further being responsive to said comparing means output signal being asserted for first causing an execution of only those buffered read requests which precede a buffered read request which caused the assertion of said comparing means output signal and then causing an execution of buffered write requests.

1.一種 MCU 用來控制資料處理系統(Data Processing System)中由至少一個記憶單元所構成的主系統記憶體(Main System Memory),其包含:

第一個介面由 MCU 和至少一個主系統記憶體 中的記憶單元組成;

第二個介面由 MCU 和系統匯流排組成,透過有訊號線傳遞包括讀取或寫入記憶體的資訊單元,系統匯流排包括一個系統位址匯流排(System Address Bus);

透過結合第一介面和第二介面回應從系統匯 流排傳遞過來的寫入要求,為了處理儲存一個 或多個以系統位址匯流排可辨識位址的資訊 單元於一個記憶單元中的寫入要求,寫入要求 的裝置 (Write Request Executing Means) 處理 收到的寫入要求,而緩衝區(Buffer Means) 有複數的儲存位置能儲存接收到的多個寫入 要求以及寫入位址,之後再處理此寫入要求; 結合第一介面和第二介面回應從系統匯流排 傳遞過來的讀取要求,為了處理儲存一個或多 個以系統位址匯流排可辨識位址的資訊單元 於一個記憶單元中的讀取要求,讀取要求的裝 置(Read Request Executing Means)處理收到 的讀取要求,而緩衝裝置(Buffer Means)有 複數的儲存位置能儲存接收到的多個讀取要 求以及讀取位址,之後再處理此讀取要求。

MCU 包含:

有兩輸入組合分別是寫入緩衝區(Write Buffer Means)及讀取要求接收裝置(Read Request

Receiving Means),用來處理接收到的讀取位 址以及存在寫入位址緩衝區內的寫入位址,比 較的裝置(Comparing Means)於目前接收到 的讀取位址有一數值是在已儲存的寫入位址 中預先決定的範圍之內時,輸出其結果; 處理讀取和寫入要求的控制裝置(Controlling Means)用來比較裝置的輸出訊號及確保不會 在寫入之前先執行所有的讀取要求,當有前述 會造成比較裝置輸出結果的狀況時,會先處理 處理該緩衝區內需寫入的要求。

## (5) 美國 5,379,379 號專利請求項 第 22 項

22. A memory control unit for controlling a main system memory of a data processing system, the main system memory being comprised of at least one memory unit, comprising: first interface means for coupling said memory control unit to the at least one memory unit of the main system memory; second interface means for coupling said memory control unit to a system bus having signal lines for expressing information units, including memory read and write requests, the system bus including a system address bus; means, coupled to said first and to said second interface means and responsive to a write request from said system bus, for executing the write request by storing one or more information units within a memory unit at an address specified by the system address bus, said write request executing means comprising write request receiving and buffer means having a plurality of storage locations capable of storing a plurality of received write requests and associated write addresses prior to execution of the write requests; means, coupled to said first and to said second interface means and responsive to a read request from said system bus, for executing the read request by reading one or more information units from a memory unit at a location specified by the system address bus, said read request executing means comprising read request receiving and buffer means having a plurality of storage locations capable of storing a plurality of received read requests and associated read addresses prior to execution of the read requests; said memory control unit comprising: means responsive to the operation of said write request receiving and buffer means and to said read request executing means for determining, at least during a time that said read request executing means is executing a buffered read request, when a predetermined number of write requests are buffered within said write request buffer means, the predetermined number being less than a maximum possible number of buffered write requests; means responsive to the operation of said determining means for causing said second interface means to assert a signal on said system bus when said determining means determines that the predetermined number of write requests are buffered within said write request buffer means, an assertion of said signal preventing a reception of further read or write requests from said system bus; and means responsive to the operation of said determining means for executing at least one buffered write request such that the remaining number of buffered write requests is less than the predetermined number.

22. 一種 MCU 用來控制一個資料處理系統(Data Processing System)中由至少一個記憶單元所構成的主系統記憶體(Main System Memory),其包含:

第一個介面由 MCU 和至少一個主系統記憶 體中的記憶單元組成;

第二個介面由 MCU 和系統匯流排組成,透 過有訊號線傳遞包括讀取或寫入記憶體的資 訊單元,系統匯流排包括一個系統位址匯流 排(System Address Bus);

透過結合第一介面和第二介面回應從系統匯

流排傳遞過來的寫入要求,為了處理儲存一個或多個以系統位址匯流排可辨識位址的資訊單元於一個記憶單元中的寫入要求,寫入要求的裝置(Write Request Executing Means)處理收到的寫入要求,而緩衝裝置(Buffer Means)有複數的儲存位置能儲存接收到的多個寫入要求以及寫入位址,之後再處理此寫入要求。

#### MCU 包含:

回應對於接收到寫入要求及緩衝區的運算, 以及要求處理裝置(Executing Means)在讀 取要求處理裝置處理緩衝區內讀取要求的時 間內,決定何時將預先決定的寫入要求數量 被緩衝至寫入要求緩衝區中,預先決定的數 量需少於最大可被放入寫入要求緩衝區中的 數量;

回應相關裝置對於造成第二介面發出訊號的 運算,當預先決定的寫入要求數量被放入寫 入要求緩衝區中會造成第二介面發出訊號, 此訊號防止系統匯流排傳來更多其他的讀取 或寫入要求;

執行至少一個被緩衝的寫入要求使在緩衝區內的寫入要求數量少於預先決定的數量。

## (6) 美國 5,379,379 號專利請求項 第 23 項

23. A memory control unit as set forth in claim 22 and further comprising means, having a first input coupled to said write buffer means and a second input coupled to said read request receiving means, for comparing a received read address to write addresses stored in said write address buffer means, said comparing means having an output signal for indicating, when asserted, an occurrence of the reception of a read address within a range of addresses of one of said stored write addresses, said memory control unit further comprising means for controlling the execution of read and write requests, said controlling means being coupled to said comparing means output signal and being responsive to said comparing means output signal

not being asserted for causing an execution of all buffered read requests before any buffered write requests, said controlling means further being responsive to said comparing means output signal being asserted for causing an execution of only those buffered read requests which precede a buffered read request which caused the assertion of said comparing means output signal and then causing an execution of buffered write requests.

23. 如請求項 22 所述之 MCU,其中另有兩輸入組合分別是寫入緩衝區(Write Buffer Means)及讀取要求接收裝置(Read Request Receiving Means),用來處理接收到的讀取位址以及存在寫入位址緩衝區內的寫入位址。比較的裝置(Comparing Means)於目前接收到的讀取位址有一數值是在已儲存的寫入位址中預先決定的範圍之內時,輸出其結果。處理讀取和寫入要求的控制裝置(Controlling Means)用來比較裝置的輸出訊號及確保不會在寫入之前先執行所有的讀取要求,當有前述會造成比較裝置輸出結果的狀況時,會先處理在此之前的所有緩衝區內的讀取要求,之後再處理該緩衝區內需寫入的要求。

## (7) 美國 5,077,733 號專利請求項 第1項

1. Apparatus for determining priority of access to a bus among a set of devices coupled to the bus, each device being represented for priority purposes by a node in a group of nodes, each node being coupled to the bus and receiving a priority line from a first adjacent node and providing a priority line to a second adjacent node and having a priority relative to a single node with the highest priority, the priority determining apparatus comprising in each node: priority logic means for permitting access to the represented device if no higher priority node has requested access; and highest priority node specification means responsive to the bus for specifying whether the node is presently the highest priority node and, if the node is presently the highest